# CA-IS322x 6A Sink/5A Source, 5.7kV<sub>RMS</sub> Isolated Dual-Channel Gate Driver

### 1. **Features**

### **Support Broad Range of Applications**

Dual low-side, dual high-side drivers

Shanghai Chipanalog Microelectronics Co., Ltd.

- Half-bridge drivers

- 6A Peak Sink Current and 5A Peak Source Current

### Wide Supply Range:

- 3V to 18V Input-side V<sub>CCI</sub> supply range

- Up to 25V V<sub>DD</sub> output drive supply with 8V and 12V precision UVLO options

### **Matching Propagation Delay**

- 56ns Propagation delay (Typ.)

- 5ns Propagation delay matching (Max.)

- 7ns Pulse width distortion(Max.)

- 20ns Minimum pulse width(Tvp.)

### **Programmable Overlap and Dead-time**

- -40°C to +125°C Operating Temperature Range

- **Robust Galvanic Isolation**

- High lifetime: >40 years

- Up to 3.75kV<sub>RMS</sub> (narrow SOIC package) or 5.7kV<sub>RMS</sub> (wide SOIC package) isolation rating

- Common-mode transient immunity (CMTI) > ±100V/ns

- Withstands up to 12.8kV surge

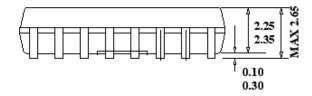

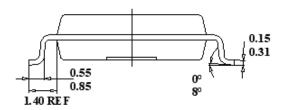

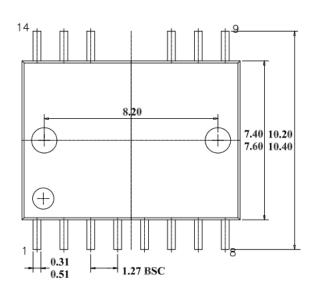

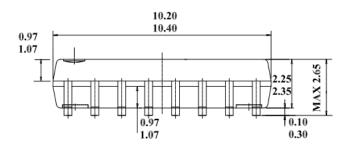

# **Package options**

- Narrow-body SOIC16(N) package

- Wide-body SOIC14(K) package

- Wide-body SOIC16(W) package

### Safety regulatory approvals

- 8000 V<sub>PK</sub> reinforced isolation per DIN V VDE V0884-11: 2017-01

- 5.7 kV<sub>RMS</sub> isolation for 1 minute according to **UL1577**

### **Applications** 2.

- Isolated DC-DC and AC-DC Converters

- Motor Control

- **LED Lighting**

- Uninterruptible Power Supply (UPS)

- Isolated Gate Driver for Inverters

- **HEV/EV Battery Charger**

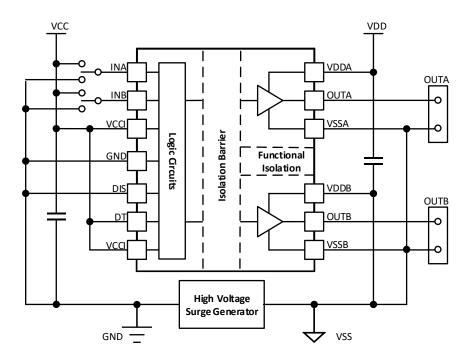

### **General Description**

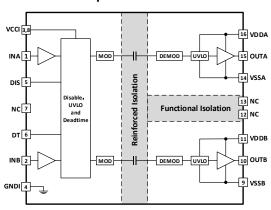

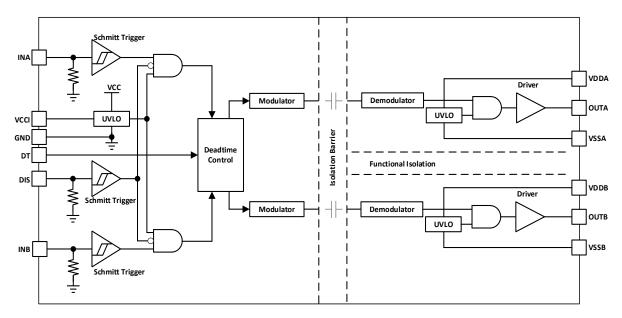

The CA-IS322x devices are a family of dual-channel isolated gate drivers capable of sinking 6A and sourcing 5A peak currents. These devices have very fast switching time, combined with short propagation delays (56ns, typ) and small pulse width distortion, making them ideal to drive power MOSFET, IGBT or silicon-carbide(SiC) transistors with up to 5MHz frequency in various inverter, isolated power supply or motor control applications.

All devices have integrated digital galvanic isolation using Chipanalog's proprietary capacitive isolation technology. They feature isolation for a withstand voltage rating of 3.75kV<sub>RMS</sub> (narrow SOIC package) or 5.7kV<sub>RMS</sub> (wide SOIC package) for 60 seconds with minimum common-mode transient immunity (CMTI) of 100V/ns. The internal functional isolation between driver A and driver B on the secondary-side (output-side) allows up to 1500V DC working voltage.

The CA-IS322x family of devices can be configured as dual low-side, dual high-side or half-bridge drivers with programmable dead-time. The enable control (EN pin for the CA-IS3222) and disable control (DIS pin for the CA-IS3221) allow both driver A and driver B outputs to be quickly set to logic-low, turning off the external power transistor. They also have a default-low output. The default is the state the output assumes when the input is either not powered or is open-circuit. Also, the driver outputs are set to logic-low when input-side or output-side supply is in UVLO, or the device is disabled.

The CA-IS322x devices accept 3V to 18V V<sub>CCI</sub> supply and up to 25V V<sub>DD</sub> wide supply range. They are available either in a 16-pin narrow-body SOIC package, or in a 16-pin and 14-pin wide-body SOIC packages. All devices are rated for operation at ambient temperatures of -40°C to +125°C.

### **Device Information**

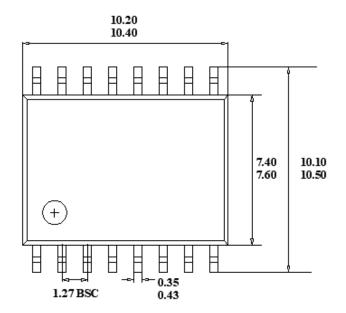

| Part Number            | Package                        | Package Size<br>(Nominal Value) |

|------------------------|--------------------------------|---------------------------------|

| CA-IS3221<br>CA-IS3222 | SOIC16-WB (W)<br>SOIC14-WB (W) | 10.3 mm x 7.5 mm                |

| CA-135222              | SOIC16-NB(N)                   | 9.9 mm x 3.9 mm                 |

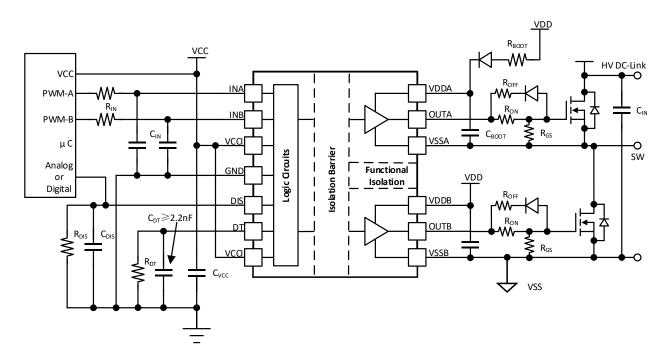

# **Simplified Schematic**

# 4. Ordering Information

**Table 4-1. Ordering Information**

| Part #      | DIS PIN / EN PIN | VDDA/VDDB UVLO Isolation Rating |                        | Package   |

|-------------|------------------|---------------------------------|------------------------|-----------|

| CA-IS3221BW | DIS              | 8                               | 5.7 kV <sub>RMS</sub>  | SOIC16-WB |

| CA-IS3221BK | DIS              | 8                               | 5.7 kV <sub>RMS</sub>  | SOIC14-WB |

| CA-IS3222BW | EN               | 8                               | 5.7 kV <sub>RMS</sub>  | SOIC16-WB |

| CA-IS3222BK | EN               | 8                               | 5.7 kV <sub>RMS</sub>  | SOIC14-WB |

| CA-IS3221CW | DIS              | 12                              | 5.7 kV <sub>RMS</sub>  | SOIC16-WB |

| CA-IS3221CK | DIS              | 12                              | 5.7 kV <sub>RMS</sub>  | SOIC14-WB |

| CA-IS3222CW | EN               | 12                              | 5.7 kV <sub>RMS</sub>  | SOIC16-WB |

| CA-IS3222CK | EN               | 12                              | 5.7 kV <sub>RMS</sub>  | SOIC14-WB |

| CA-IS3221BN | DIS              | 8                               | 3.75 kV <sub>RMS</sub> | SOIC16-NB |

| CA-IS3222BN | EN               | 8                               | 3.75 kV <sub>RMS</sub> | SOIC16-NB |

| CA-IS3221CN | DIS              | 12                              | 3.75 kV <sub>RMS</sub> | SOIC16-NB |

| CA-IS3222CN | EN               | 12                              | 3.75 kV <sub>RMS</sub> | SOIC16-NB |

# **Table of Contents**

| 1. |       | ıres                                         |     |

|----|-------|----------------------------------------------|-----|

| 2. | Appli | cations                                      | 1   |

| 3. | Gene  | ral Description                              | 1   |

| 4. | Orde  | ring Information                             | 2   |

| 5. | Revis | ion History                                  | 3   |

| 6. | Pin C | onfiguration and Description                 | 4   |

|    | 6.1.  | CA-IS3221 Pin Configuration and Description  | 4   |

|    | 6.2.  | CA-IS3222 Pin Configuration and Description  | 5   |

| 7. | Speci | fications                                    | 6   |

|    | 7.1.  | Absolute Maximum Ratings <sup>1</sup>        | 6   |

|    | 7.2.  | ESD Ratings                                  | 6   |

|    | 7.3.  | Recommended Operating Conditions             | 6   |

|    | 7.4.  | Thermal Information                          | 6   |

|    | 7.5.  | Power Ratings                                |     |

|    | 7.6.  | Insulation Specifications                    |     |

|    | 7.7.  | Safety-Related Certifications                | 8   |

|    | 7.8.  | Safety Limits                                | 8   |

|    | 7.9.  | Electrical Characteristics                   |     |

|    | 7.10. | Switching Characteristics                    |     |

|    | 7.11. | Typical Characteristics                      |     |

| 8. | Parar | meter Measurement Information                |     |

|    | 8.1.  | Propagation Delay and Pulse Width Distortion |     |

|    | 8.2.  | Rise Time and Fall Time                      | .13 |

|    | 8.3.  | Input and Disable Signals Response Time      | .13 |

Shanghai Chipanalog Microelectronics Co., Ltd.

|     | 8.4.   | Programmable Dead-time            | 14 |

|-----|--------|-----------------------------------|----|

|     | 8.5.   | Power-up UVLO Delay               | 14 |

|     | 8.6.   | CMTI Test Circuit                 | 15 |

| 9.  | Detail | ed Description                    | 16 |

|     | 9.1.   | Overview                          | 16 |

|     | 9.2.   | Input Stage                       | 17 |

|     | 9.2.   | 1. TTL and CMOS compatible inputs | 17 |

|     | 9.2.   | 2. Enable and Disable Control     | 17 |

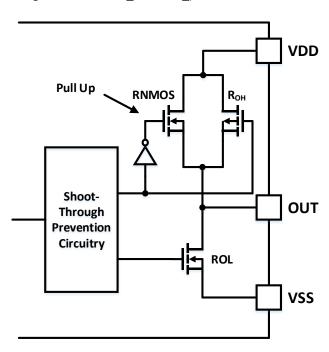

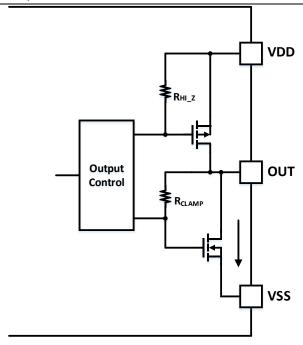

|     | 9.3.   | Driver Output Stage               | 18 |

|     | 9.4.   | Undervoltage Lockout (UVLO)       | 18 |

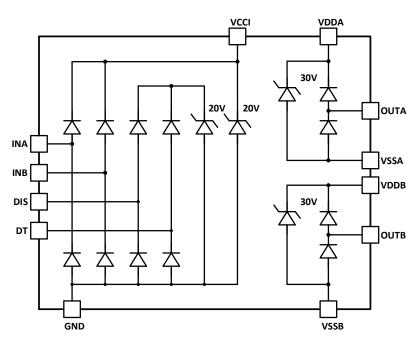

|     | 9.5.   | Digital Isolation                 | 20 |

|     | 9.6.   | ESD Protection Structure          | 20 |

|     | 9.7.   | Programmable Dead-time            | 20 |

| 10. | Applic | ation and Implementation          | 22 |

|     | 10.1.  | Typical Application               | 22 |

|     | 10.2.  | Power Supply                      | 23 |

|     | 10.3.  | Input Filter Selection            | 23 |

|     | 10.4.  | Gate Resistance Selection         | 23 |

|     | 10.5.  | PCB Layout                        | 24 |

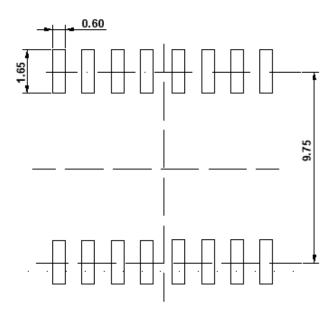

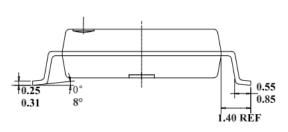

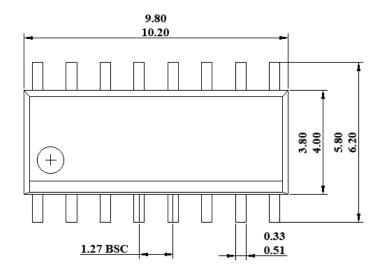

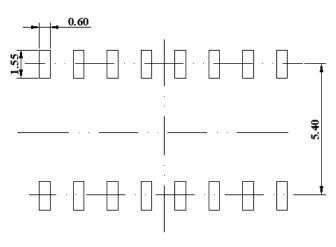

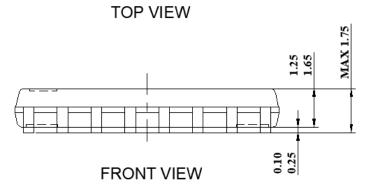

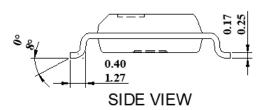

| 11. | Packag | ge Information                    | 25 |

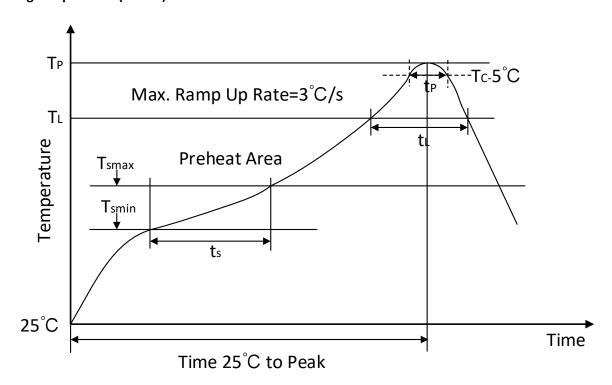

| 12. | Solder | ring Temperature (reflow) Profile | 28 |

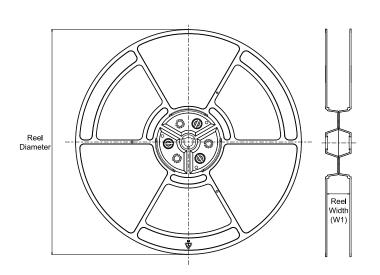

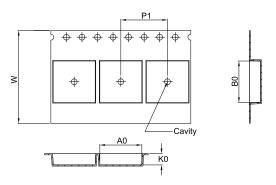

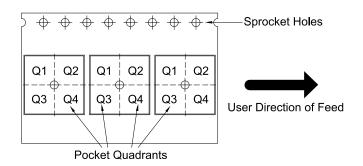

| 13. |        | and Reel Information              |    |

| 14. |        | tant statement                    |    |

|     | mpoi   | tailt 3tateilleile                | 50 |

# **Revision History**

| Revision Number     | Description | Page Changed |

|---------------------|-------------|--------------|

| Preliminary Version | N/A         | N/A          |

# 6. Pin Configuration and Description

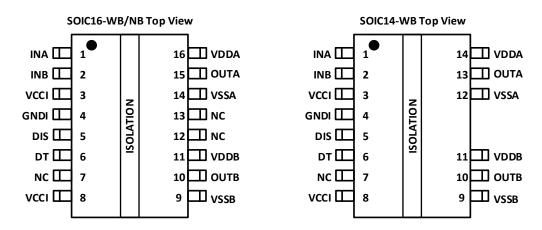

# 6.1. CA-IS3221 Pin Configuration and Description

Figure 6-1. The CA-IS3221 Pin Configuration (SOIC16/SOIC14 Package)

Table 6-1. The CA-IS3221 Pin Description

|          | Pin Nu                           | mber           |                                                                                                                                                              |                                                                                                                     |

|----------|----------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Pin Name | CA-IS3221BW/CW<br>CA-IS3221BN/CN | CA-IS3221BK/CK | Туре                                                                                                                                                         | Description                                                                                                         |

| INA      | 1                                | 1              | Input                                                                                                                                                        | Driver A input. INA is TTL/CMOS compatible and has internal pulldown to GNDI. Connect this pin to GNDI if not used. |

| INB      | 2                                | 2              | Input                                                                                                                                                        | Driver B input. INB is TTL/CMOS compatible and has internal pulldown to GNDI. Connect this pin to GNDI if not used. |

| VCCI     | 3, 8                             | 3, 8           | Power Supply 3 V to 18 V power supply input for input side. Bypass VCCI to GNDI with an at least 0.1µF capacitor as close to the device as possible.         |                                                                                                                     |

| GNDI     | 4                                | 4              | Ground                                                                                                                                                       | Ground reference for input-side                                                                                     |

|          |                                  |                |                                                                                                                                                              | Disable input on input-side. Drive DIS high to disable isolator and put                                             |

| DIS      | 5                                | 5              | Logic Input                                                                                                                                                  | driver output low; Drive DIS low or leave open, enable gate driver. DIS                                             |

|          |                                  |                |                                                                                                                                                              | has internal pull-down to GNDI. Connect this pin to GNDI if not used.                                               |

|          |                                  |                |                                                                                                                                                              | Programmable dead-time input. Connecting DT to V <sub>CCI</sub> allows the output                                   |

|          | 6                                | 6              | Input                                                                                                                                                        | to overlap; Placing a $500\Omega$ to $500k\Omega$ resistor between DT and GNDI                                      |

| DT       |                                  |                |                                                                                                                                                              | adjusts dead time according to $t_{DT}(ns)=10 \times R_{DT}$ ( $k\Omega$ ). We recommended                          |

|          |                                  |                |                                                                                                                                                              | to bypass DT to GNDI with an at least 2.2nF ceramic capacitor as close to                                           |

|          |                                  |                |                                                                                                                                                              | pin DT and resistor RDT as possible. This Pin cannot be floating.                                                   |

| NC       | 7, 12, 13                        | 7              |                                                                                                                                                              | No internal connection.                                                                                             |

| VSSB     | 9                                | 9              | Ground                                                                                                                                                       | Ground reference for output-side (driver B).                                                                        |

| OUTB     | 10                               | 10             | Output                                                                                                                                                       | Gate driver output B.                                                                                               |

| VDDB     | 11                               | 11             | Power Supply                                                                                                                                                 | Power supply input for output-side (driver B). Bypass VDDB to VSSB with                                             |

| VDDB     | 11                               | 11             | rower supply                                                                                                                                                 | 0.1μF  10μF capacitors as close as possible to the pin VDDB.                                                        |

| VSSA     | 14                               | 12             | Ground Ground reference for output-side (driver A).                                                                                                          |                                                                                                                     |

| OUTA     | 15                               | 13             | Output                                                                                                                                                       | Gate driver output A.                                                                                               |

| VDDA     | 16                               | 14             | Power Supply Power supply input for output-side (driver A). Bypass VDDA to VSSA with $0.1\mu$ F  10 $\mu$ F capacitors as close as possible to the pin VDDA. |                                                                                                                     |

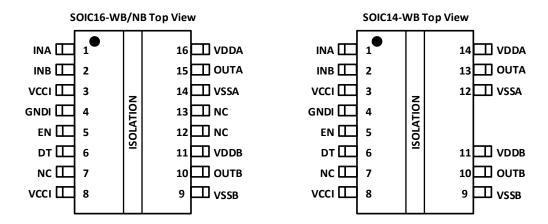

# 6.2. CA-IS3222 Pin Configuration and Description

Figure 6-2. The CA-IS3222 Pin Configuration (SOIC16/SOIC14 Package)

Table 6-2. The CA-IS3222 Pin Description

|          | Pin Number                       |                |                 |                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----------|----------------------------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | CA-IS3222BW/CW<br>CA-IS3222BN/CN | CA-IS3222BK/CK | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                   |  |

| INA      | 1                                | 1              | Input           | Driver A input. INA is TTL/CMOS compatible and has internal pull-down to GNDI. Connect this pin to GNDI if not used.                                                                                                                                                                                                                                                                          |  |

| INB      | 2                                | 2              | Input           | Driver B input. INB is TTL/CMOS compatible and has internal pull-down to GNDI. Connect this pin to GNDI if not used.                                                                                                                                                                                                                                                                          |  |

| VCCI     | 3, 8                             | 3, 8           | Power<br>Supply | 3 V to 18 V power supply input for input side. Bypass V <sub>CCI</sub> to GNDI with an at least 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                           |  |

| GNDI     | 4                                | 4              | Ground          | Ground reference for input-side.                                                                                                                                                                                                                                                                                                                                                              |  |

| EN       | 5                                | 5              | Logic Input     | Active-high enable input on input-side. Drive EN low or connect to GNDI to disable isolator and put driver output low; Drive EN high or leave open, enable gate driver. EN has internal pull-up to VCCI. Connect this pin to V <sub>CCI</sub> if not used.                                                                                                                                    |  |

| DT       | 6                                | 6              | Input           | Programmable dead-time input. Connecting DT to $V_{CCI}$ allows the output to overlap; Placing a $500\Omega$ to $500k\Omega$ resistor between DT and GNDI adjusts dead time according to $t_{DT}(ns)=10$ x $R_{DT}$ ( $k\Omega$ ). We recommended to bypass DT to GNDI with an at least 2.2nF ceramic capacitor as close to pin DT and resistor RDT as possible. This Pin cannot be floating. |  |

| NC       | 7, 12, 13                        | 7              |                 | No internal connection.                                                                                                                                                                                                                                                                                                                                                                       |  |

| VSSB     | 9                                | 9              | Ground          | Ground reference for output-side (driver B).                                                                                                                                                                                                                                                                                                                                                  |  |

| OUTB     | 10                               | 10             | Output          | Gate driver output B.                                                                                                                                                                                                                                                                                                                                                                         |  |

| VDDB     | 11                               | 11             | Power<br>Supply | Power supply input for output-side (driver B). Bypass VDDB to VSSB with $0.1\mu\text{F} \mid 10\mu\text{F}$ capacitors as close as possible to the pin VDDB.                                                                                                                                                                                                                                  |  |

| VSSA     | 14                               | 12             | Ground          | Ground reference for output-side (driver A).                                                                                                                                                                                                                                                                                                                                                  |  |

| OUTA     | 15                               | 13             | Output          | Gate driver output A.                                                                                                                                                                                                                                                                                                                                                                         |  |

| VDDA     | 16                               | 14             | Power<br>Supply | Power supply input for output-side (driver A). Bypass VDDA to VSSA with 0.1μF   10μF capacitors as close as possible to the pin VDDA.                                                                                                                                                                                                                                                         |  |

# 7. Specifications

# 7.1. Absolute Maximum Ratings<sup>1</sup>

over operating free-air temperature range unless otherwise specified. <sup>1</sup>

|                                     | Parameters                                    | Minimum | Maximum               | Unit |

|-------------------------------------|-----------------------------------------------|---------|-----------------------|------|

| Power supply voltage on input-side  | VCCI to GNDI                                  | -0.3    | 20                    | V    |

| Power supply voltage on output-side | VDDA-VSSA, VDDB-VSSB                          | -0.3    | 30                    | V    |

|                                     | OUTA to VSSA, OUTB to VSSB                    | -0.3    | V <sub>DDA</sub> +0.3 |      |

| Driver output                       | OUTA to VSSA, OUTB to VSSB                    | -0.5    | $V_{DDB}$ +0.3        | V    |

| Driver output                       | OUTA to VSSA, OUTB to VSSB, 200ns transient.  | -2      | V <sub>DDA</sub> +0.3 | V    |

|                                     | OOTA to VSSA, OOTB to VSSB, 200113 transient. | -2      | $V_{DDB}$ +0.3        |      |

| Input signals                       | INA, INB, DIS, DT to GND                      | -0.3    | V <sub>CCI</sub> +0.3 | V    |

| input signals                       | INA, INB, 50ns transient.                     | -5      | V <sub>CCI</sub> +0.3 | V    |

| Channel to channel voltage          | VSSA-VSSB, VSSB-VSSA                          |         | 1500                  | V    |

| Junction temperature <sup>2</sup>   |                                               | -40     | 150                   | °C   |

| Storage temperature                 |                                               | -65     | 150                   | °C   |

### Notes:

- 1. The stresses listed under "Absolute Maximum Ratings" are stress ratings only, not for functional operation condition. Exposure to absolute maximum rating conditions for extended periods may cause permanent damage to the device.

- 2. To maintain the recommended operating junction temperature conditions, see Thermal Information.

# 7.2. ESD Ratings

|                            |                                                     |                         |                                                                  | Value | Unit |

|----------------------------|-----------------------------------------------------|-------------------------|------------------------------------------------------------------|-------|------|

| V Flootus static dischause | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001. | ±4000                   | V                                                                |       |      |

|                            | $V_{ESD}$                                           | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101. | ±1000 | V    |

# 7.3. Recommended Operating Conditions

Over operating free-air temperature range unless otherwise specified.

|                       | Parameters                                                             | Minimum         | Maximum | Unit |    |

|-----------------------|------------------------------------------------------------------------|-----------------|---------|------|----|

| V <sub>CCI</sub>      | Power supply voltage on input-side                                     |                 | 3       | 18   | V  |

| V V                   | Power supply voltage on output-side  8V UVLO version  12V UVLO version | 8V UVLO version | 10      | 25   | V  |

| $V_{DDA}$ , $V_{DDB}$ |                                                                        | 14              | 25      | V    |    |

| T <sub>J</sub>        | Junction temperature                                                   |                 | -40     | 130  | °C |

| T <sub>A</sub>        | Ambient temperature                                                    |                 | -40     | 125  | °C |

### 7.4. Thermal Information

|                 |                                        | CA-IS                  | 322x      |      |

|-----------------|----------------------------------------|------------------------|-----------|------|

|                 | Thermal Metric                         | SOIC16-WB<br>SOIC14-WB | SOIC16-NB | Unit |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 67.3                   | 96.2      | °C/W |

### 7.5. Power Ratings

| Parameters      |                                            | Test Conditions                                                  | Typical Value | Unit |

|-----------------|--------------------------------------------|------------------------------------------------------------------|---------------|------|

| $P_D$           | Maximum input and output power dissipation | V <sub>CCI</sub> = 18V, V <sub>DDA</sub> =V <sub>DDB</sub> =15V, | 1.05          | W    |

| P <sub>D1</sub> | Maximum input power dissipation            | INA/INB=3.3V, 3MHz square wave with 50% duty cycle, $C_L = 1nF$  | 0.05          | W    |

| $P_{D2}$        | Maximum output power dissipation           | with 30% duty cycle, C[ = 111F                                   | 0.5           | W    |

# 7.6. Insulation Specifications

| Dama wa aka wa    |                                                   | Took Conditions                                                                                                                                                                  | Specifi | Hait            |                  |

|-------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|------------------|

|                   | Parameters                                        | Test Conditions                                                                                                                                                                  | W       | N               | Unit             |

| CLR               | External clearance                                | Shortest terminal-to-terminal distance through air                                                                                                                               | >8      | >4              | mm               |

| CPG               | External creepage                                 | Shortest terminal-to-terminal distance across the package surface                                                                                                                | >8      | >4              | mm               |

| DTI               | Distance through the insulation                   | Minimum internal gap (internal clearance)                                                                                                                                        | > 28    |                 | μm               |

| CTI               | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                            | > (     | 500             | V                |

|                   | Material group                                    | According to IEC 60664-1                                                                                                                                                         |         | I               |                  |

|                   | 170 0000 A                                        | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                       | I-      | IV              |                  |

|                   | IEC 60664-1 over-voltage category                 | Rated mains voltage ≤ 400 V <sub>RMS</sub>                                                                                                                                       | Į-      | ·III            |                  |

| DIN V V           | DE V 0884-11:2017-01 <sup>1</sup>                 |                                                                                                                                                                                  | I.      |                 |                  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                                                                                                                             | 2121    | 566             | $V_{PK}$         |

| V <sub>IOWM</sub> | Maximum operating isolation voltage               | AC voltage; time-dependent dielectric breakdown (TDDB) test                                                                                                                      | 1500    | 400             | V <sub>RMS</sub> |

|                   | , ,                                               | DC voltage                                                                                                                                                                       | 2121    | 566             | V <sub>DC</sub>  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage               | $V_{TEST} = V_{IOTM}$ , t=60 s (qualification);<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , t=1 s (100% product test)                                                                  | 8000    | 5300            | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>2</sup>      | Test method per IEC 60065, 1.2/50 $\mu$ s waveform, $V_{TEST} = 1.6 \times V_{IOSM} \text{ (production test)}$                                                                   |         | 5300            | V <sub>PK</sub>  |

|                   |                                                   | Method a, after input/output safety tests subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10s$                                 |         | ≤5              |                  |

| $q_{pd}$          | Apparent charge <sup>3</sup>                      | Method a, after environmental tests subgroup 1, $V_{ini} = V_{IOTM}, t_{ini} = 60s;$ $V_{pd(m)} = 1.6 \times V_{IORM}, t_m = 10s$                                                | ≤5      |                 | pC               |

|                   |                                                   | Method b1, at routine test (100% production test) and preconditioning (sample test) $V_{ini} = 1.2 \times V_{IOTM}, t_{ini} = 1s;$ $V_{pd(m)} = 1.875 \times V_{IORM}, t_m = 1s$ |         | £5              |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>4</sup> | $V_{10} = 0.4 \times \sin(2\pi ft), f = 1 \text{ MHz}$                                                                                                                           | 0.5     |                 | pF               |

| -                 |                                                   | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                   | >1      | .012            | ·                |

| R <sub>IO</sub>   | Isolation resistance, input to output4            | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                          | >1      | .011            | Ω                |

|                   |                                                   | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                | >1      | LO <sup>9</sup> |                  |

|                   | Pollution degree                                  |                                                                                                                                                                                  |         | 2               |                  |

|                   | Climatic category                                 |                                                                                                                                                                                  | 40/1    | 25/21           |                  |

| UL 1577           |                                                   | ·                                                                                                                                                                                | •       |                 |                  |

| V <sub>ISO</sub>  | Maximum isolation voltage                         | $V_{TEST} = V_{ISO}$ , t = 60 s (certified)<br>$V_{TEST} = 1.2 \times V_{ISO}$ , t = 1 s (100% production test)                                                                  | 5700    | 3750            | V <sub>RMS</sub> |

### Notes:

- 1. This coupler is suitable for "safe electrical insulation" only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- 2. Devices are immersed in oil during surge characterization.

- 3. The characterization charge is discharging charge (pd) caused by partial discharge.

- 4. Capacitance and resistance are measured with all pins on field-side and logic-side tied together.

# 7.7. Safety-Related Certifications

| VDE (pending)                                                   | UL (pending)                                       | CQC (pending)                                 |

|-----------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------|

| Certified according to DIN V VDE V                              | Certified according to UL 1577 Component           | Certified according to                        |

| 0884-11:2017-01                                                 | Recognition Program                                | GB4943.1-20111                                |

| Reinforced isolation(SOIC16-WB/SOIC14-WB):                      | Protection voltage:                                | Reinforced insulation,                        |

| Maximum transient isolation voltage: 8000V <sub>pk</sub>        | - 3750V <sub>RMS</sub> for SOIC16-NB package       | 1500 V <sub>RMS</sub> maximum working voltage |

| Maximum repetitive-peak isolation voltage: 2121 V <sub>pk</sub> | - 5700V <sub>RMS</sub> for SOIC14-WB and SOIC16-WB | (Altitude ≤ 5000 m)                           |

| Maximum surge isolation voltage: 8000V <sub>pk</sub>            | packages                                           |                                               |

| Basic isolation (SOIC16-NB):                                    |                                                    |                                               |

| Maximum transient isolation voltage: 5300V <sub>pk</sub>        |                                                    |                                               |

| Maximum repetitive-peak isolation voltage: 566 V <sub>pk</sub>  |                                                    |                                               |

| Maximum surge isolation voltage: 5000V <sub>pk</sub>            |                                                    |                                               |

| Certificate Number: pending                                     | Certificate Number: pending                        | Certificate Number: pending                   |

# 7.8. Safety Limits

| Parameters |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Test Conditions                                                                                         |                       | Minimum | Typical | Maximum | Unit     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|---------|---------|---------|----------|

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $R_{qJA} = 67.3^{\circ}C/W$ , $V_{DDA} = V_{DDB} = 15V$ ,<br>$T_1 = 150^{\circ}C$ , $T_A = 25^{\circ}C$ | Driver A,<br>Driver B |         | 75      |         |          |

| Is         | Safety output supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $R_{qJA} = 67.3^{\circ}C/W, V_{DDA} = V_{DDB} =$                                                        | Driver A,             |         |         | 26      | mA       |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25V,T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                                                       | Driver B              |         | 36      |         | <u> </u> |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         | Input                 |         |         | 50      |          |

| Ps         | Safety power dissipation $R_{qJA} = 67.3$ °C/W, $T_J = 150$ °C, $T_A = 150$ °C, $T_{A} = 150$ °C, $T_$ | Driver A                                                                                                |                       |         | 900     | mW      |          |

| FS         | Salety power dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25°C                                                                                                    | Driver B              |         |         | 900     | 11100    |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         | Total                 |         |         | 1850    |          |

| Ts         | Maximum safety temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |                       |         |         | 150     | °C       |

# 7.9. Electrical Characteristics

$T_A = -40$ °C to +125°C,  $V_{CCI} = 3.3$ V or 5V, connect a  $0.1\mu$ F bypass capacitor between VCCI and GNDI;  $V_{DDA} = V_{DDB} = 15$ V, Connect a  $1\mu$ F bypass capacitor between VDDA and VSSA, between VDDB and VSSB, respectively, unless otherwise noted. Typical values are at  $T_A = +25$ °C, unless otherwise noted.

|                                                           | Parameters                                            | Test Conditions                                                                                                                   | Minimum     | Typical       | Maximum    | Unit |

|-----------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|------------|------|

| Supply Current                                            |                                                       |                                                                                                                                   |             |               |            |      |

| I <sub>VCCI</sub>                                         | V <sub>CCI</sub> quiescent current                    | $V_{INA} = 0 V$ , $V_{INAB} = 0 V$                                                                                                |             | 1.5           | 2.0        | mA   |

| $I_{VDDA}$ , $I_{VDDB}$                                   | V <sub>DDA</sub> / V <sub>DDB</sub> quiescent current | $V_{INA} = 0 V$ , $V_{INAB} = 0 V$                                                                                                |             | 1.0           | 1.8        | mA   |

| l <sub>vcci</sub>                                         | V <sub>CCI</sub> operating current                    | (f = 500 kHz) current per channel, C <sub>OUT</sub> = 100 pF                                                                      |             | 2.0           |            | mA   |

| Ivdda,Ivddb                                               | V <sub>DDA</sub> /V <sub>DDB</sub> operating current  | (f = 500 kHz) current per channel, $C_{OUT}$ = 100 pF                                                                             |             | 3.0           |            | mA   |

| V <sub>CCI</sub> Undervoltage-                            | Lockout Threshold                                     |                                                                                                                                   |             |               |            |      |

| V <sub>VCCI(UVLO+)</sub>                                  | V <sub>CCI</sub> rising                               | INA,INB,DT tied to VCCI, VCCI rising                                                                                              | 2.55        | 2.7           | 2.85       | V    |

| V <sub>VCCI(UVLO-)</sub>                                  | V <sub>CCI</sub> falling                              | INA,INB,DT tied to VCCI, VCCI falling                                                                                             | 2.25        | 2.4           | 2.55       | V    |

| V <sub>VCCI_HYS(UVLO)</sub>                               | Undervoltage-lockout threshold hysteresis             |                                                                                                                                   |             | 0.3           |            | ٧    |

| VDD_ Undervoltag                                          | e-Lockout Threshold (8V UVLO version                  | on)                                                                                                                               | _           |               |            |      |

| V <sub>VDDA(UVLO+)</sub> V <sub>VDDB(UVLO+)</sub>         | V <sub>DDA</sub> /V <sub>DDB</sub> rising             | VCCI=INA=INB=DT, VDD rising                                                                                                       | 7.3         | 8.1           | 8.9        | V    |

| V <sub>VDDA</sub> (UVLO-)                                 | V <sub>DDA</sub> /V <sub>DDB</sub> falling            | VCCI=INA=INB=DT, VDD falling                                                                                                      | 6.7         | 7.4           | 8.2        | V    |

| V <sub>VDDA_HYS</sub> (UVLO) V <sub>VDDB_HYS</sub> (UVLO) | Undervoltage-lockout threshold hysteresis             |                                                                                                                                   |             | 0.7           |            | ٧    |

|                                                           | e-Lockout Threshold (12V UVLO versi                   | ion)                                                                                                                              |             |               |            |      |

| V <sub>VDDA(UVLO+)</sub>                                  | V <sub>DDA</sub> /V <sub>DDB</sub> rising             | VCCI=INA=INB=DT, VDD rising                                                                                                       | 10.9        | 12.1          | 13.3       | V    |

| V <sub>VDDA(UVLO-)</sub> V <sub>VDDB(UVLO-)</sub>         | V <sub>DDA</sub> /V <sub>DDB</sub> falling            | VCCI=INA=INB=DT, VDD falling                                                                                                      | 9.9         | 11.1          | 12.3       | V    |

| V <sub>VDDA_HYS</sub> (UVLO) V <sub>VDDB_HYS</sub> (UVLO) | Undervoltage-lockout threshold hysteresis             |                                                                                                                                   |             | 1.0           |            | V    |

| Logic Input (INA, IN                                      | NB and DISABLE)                                       |                                                                                                                                   |             |               |            |      |

| V <sub>INAH</sub> , V <sub>INBH</sub> , V <sub>DISH</sub> | Input high voltage                                    | VIN rising                                                                                                                        | 1.6         | 1.8           | 2          | V    |

| V <sub>INAL</sub> , V <sub>INBL</sub> , V <sub>DISL</sub> | Input low voltage                                     | VIN falling                                                                                                                       | 0.8         | 1             | 1.2        | V    |

| VINA_HYS, VINBL_HYS, VDIS_HYS                             | Input hysteresis                                      | VIIVIAIIII                                                                                                                        | 0.0         | 0.8           | 1.2        | V    |

| V <sub>INA</sub> , V <sub>INB</sub>                       | Negative transient, referenced to GND, 50 ns pulse    |                                                                                                                                   | -5          |               |            | V    |

| Driver Output                                             | ·                                                     |                                                                                                                                   |             |               |            |      |

| Іона, Іонв                                                | Peak output current                                   | C <sub>VDD</sub> = 10 μF, C <sub>LOAD</sub> = 0.18 μF, f = 1 kHz,                                                                 |             | 5             |            | Α    |

|                                                           | Peak output current                                   | $C_{VDD} = 10 \ \mu\text{F}, \ C_{LOAD} = 0.18 \ \mu\text{F}, \ f = 1 \ \text{kHz},$                                              |             | 6             |            | - '  |

| I <sub>OLA</sub> , I <sub>OLB</sub>                       | reak output current                                   |                                                                                                                                   |             | 0             |            |      |

| R <sub>OHA</sub> , R <sub>OHB</sub>                       | Output resistance at high                             | I <sub>OUT</sub> = -10 mA, T <sub>A</sub> = 25°C, R <sub>OHA</sub> , R <sub>OHB</sub> do not represent drive pull-up performance. |             | 5             |            | Ω    |

| R <sub>OLA</sub> , R <sub>OLB</sub>                       | Output resistance at low                              | I <sub>OUT</sub> = 10 mA, T <sub>A</sub> = 25°C                                                                                   |             | 0.55          |            | Ω    |

| V <sub>OHA</sub> , V <sub>OHB</sub>                       | Output voltage at high                                | $V_{DDA}/V_{DDB} = 15V$ , $I_{OUT} = -10$ mA, $T_A = 25$ °C                                                                       |             | 14.95         |            | V    |

| V <sub>OLA</sub> , V <sub>OLB</sub>                       | Output voltage at low                                 | $V_{DDA}/V_{DDB} = 15V$ , $I_{OUT} = 10$ mA, $T_A = 25$ °C                                                                        |             | 5.5           |            | mV   |

| Dead-time and Ove                                         | erlap                                                 |                                                                                                                                   |             |               |            |      |

| 5 1                                                       | Connect pin DT to V <sub>CCI</sub>                    |                                                                                                                                   | Overlap tin | ne is up to I | NA and INB |      |

| Dead-time                                                 | $R_{DT} = 20 \text{ k}\Omega$ , See Figure 8-4        |                                                                                                                                   | 160         | 200           | 240        | ns   |

# 7.10. Switching Characteristics

$T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{CCI} = 3.3\text{V}$  or 5V, connect a  $0.1\mu\text{F}$  bypass capacitor between VCCI and GNDI;  $V_{DDA} = V_{DDB} = 15\text{V}$ , Connect a  $1\mu\text{F}$  bypass capacitor between VDDA and VSSA, between VDDB and VSSB, respectively, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.

|                           | Parameters                                                                          | Test Conditions                                                                                                                                   | Minimum | Typical | Maximum | Unit |

|---------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|------|

| t <sub>r</sub>            | Output rise time                                                                    | - C <sub>OUT</sub> = 1.8 nF, See Figure 8-2                                                                                                       |         | 6       | 16      | ns   |

| t <sub>f</sub>            | Output fall time                                                                    | C <sub>007</sub> – 1.8 Hr, See Figure 8-2                                                                                                         |         | 7       | 12      | ns   |

| t <sub>PWmin</sub>        | Minimum pulse width                                                                 | Output off if t <sub>PW</sub> less than minimum value, No load                                                                                    | 20      |         | ns      |      |

| $t_{\mathtt{PLH}}$        | Propagation delay, low to high                                                      | f <sub>PWM</sub> = 100kHz, No Load,<br>See Figure 8-1                                                                                             |         | 56 100  |         | ns   |

| t <sub>PHL</sub>          | Propagation delay, high to low                                                      | f <sub>PWM</sub> = 100kHz, No Load,<br>See Figure 8-1                                                                                             |         | 56      | 100     | ns   |

| t <sub>PWD</sub>          | Pulse width distortion  t <sub>PHL</sub> -t <sub>PLH</sub>                          | t <sub>PWD=</sub>  t <sub>PHL</sub> -t <sub>PLH</sub>  , No Load,<br>See Figure 8-1                                                               |         |         | 7       | ns   |

| $t_{DM}$                  | Channel to channel propagation delay matching                                       | t <sub>DM</sub> =  t <sub>PHLA</sub> -t <sub>PHLB</sub>   or  t <sub>PLHA</sub> -t <sub>PLHB</sub>  <br>f <sub>PWM</sub> = 100kHz, See Figure 8-1 |         |         | 5       | ns   |

| t <sub>VCCI+ to OUT</sub> | V <sub>CCI</sub> power up delay time:<br>UVLO rise to OUTA, OUTB                    | INA or INB is connected to VCCI<br>See Figure 8-5                                                                                                 |         | 55      | 100     | μs   |

| t <sub>VDD_+ to OUT</sub> | V <sub>DDA</sub> , V <sub>DDB</sub> power up delay time:<br>UVLO rise to OUTA, OUTB | INA or INB is connected to VCCI<br>See Figure 8-5                                                                                                 |         | 68      | 100     | μs   |

| CMTI <sub>H</sub>         | CMTI (output high)                                                                  | INA = INB = VCCI; V <sub>CM</sub> = 1500V,<br>See Figure 8-6                                                                                      | 100     | 150     |         | V/ns |

| CMTI <sub>L</sub>         | CMTI (output low)                                                                   | INA = INB = GNDI; V <sub>CM</sub> = 1500V,<br>See Figure 8-6                                                                                      | 100     | 150     |         | V/ns |

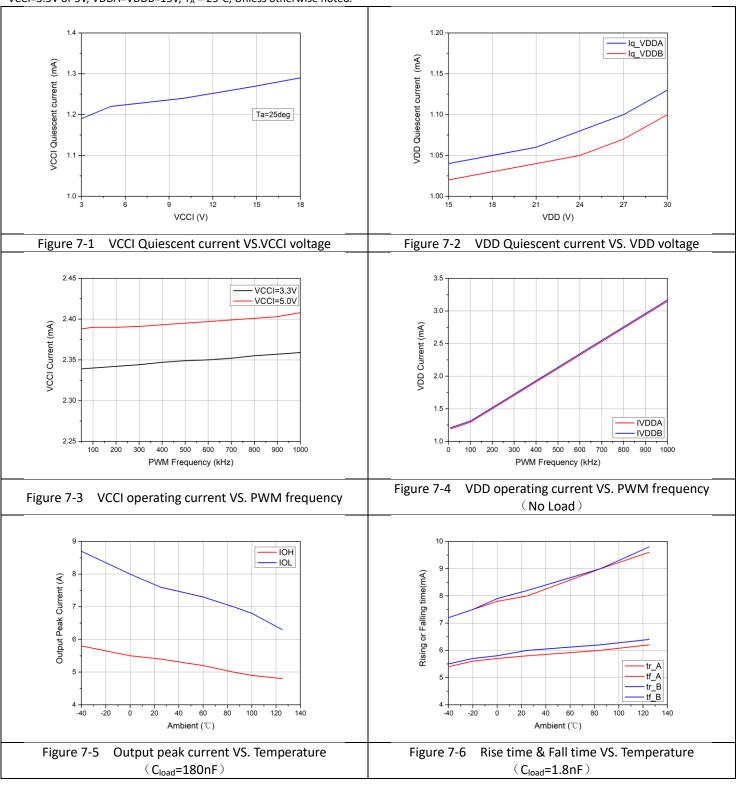

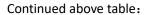

### 7.11. Typical Characteristics

VCCI=3.3V or 5V, VDDA=VDDB=15V, T<sub>A</sub> = 25°C, Unless otherwise noted.

### 8. Parameter Measurement Information

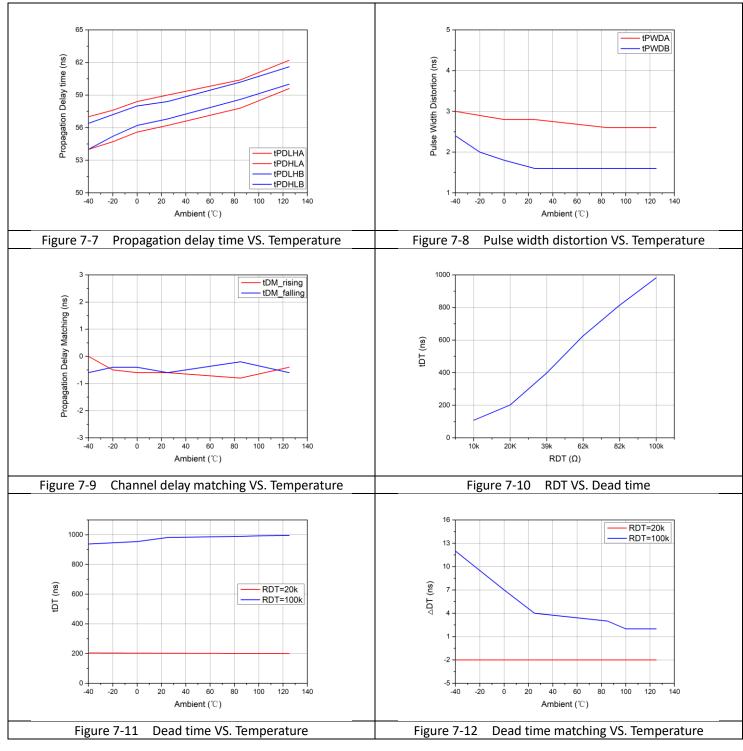

# 8.1. Propagation Delay and Pulse Width Distortion

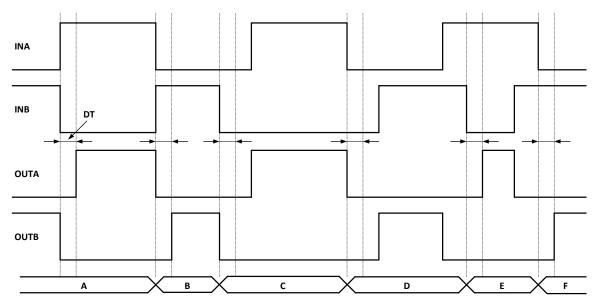

Figure 8-1 shows the definition and measurement for the pulse width distortion( $t_{PWD}$ ) and propagation delay matching between channel A and channel B ( $t_{DM}$ ). Ensure that both inputs are in phase and disabled the dead time function by shorting the DT pin to VCCI during measurement.

Figure 8-1. Propagation delay and pulse width distortion timing diagram (overlapping input and dead-time disabled)

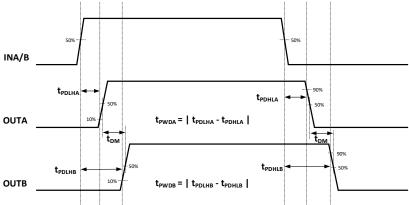

### 8.2. Rise Time and Fall Time

Figure 8-2 shows the definition of rising time (t<sub>r</sub>) and falling time (t<sub>f</sub>).

Figure 8-2. Rise time and fall time

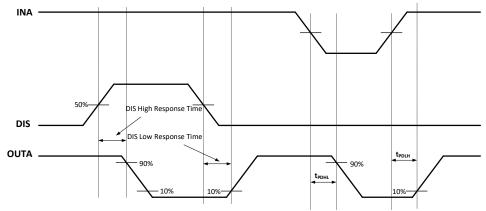

# 8.3. Input and Disable Signals Response Time

Figure 8-3 shows the disable signal response timing. Bypass DIS pin to GNDI with a 1nF low-ESR/low-ESL capacitor close to DIS pin if connecting to a micro-controller with distance.

Figure 8-3. Disable timing diagram

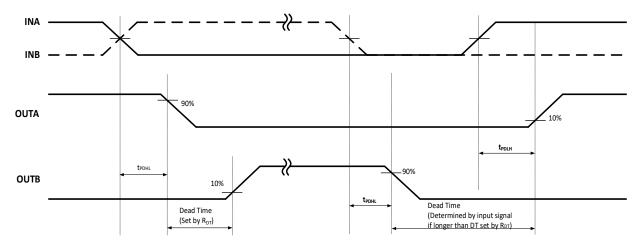

### 8.4. Programmable Dead-time

Figure 8-4 shows the dead-time measurement. Leaving pin DT open or connecting an external resistor  $R_{DT}$  between DT and GNDI sets the dead-time. For more details, please see Programmable Dead-time section .

Figure 8-4. Dead-time switching parameters

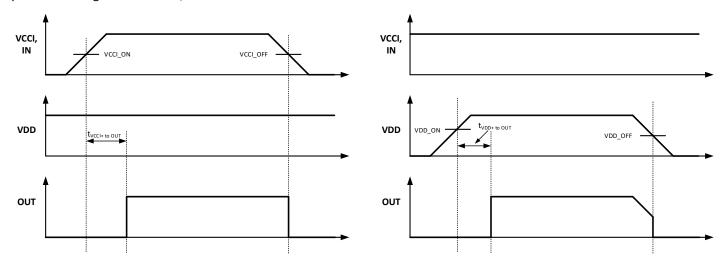

### 8.5. Power-up UVLO Delay