# **CA-IS3821** High-Performance Reinforced Dual-Channel Digital Isolators

# 1. Key Features

Signal Rate: DC to 150Mbps

Wide Operating Supply Voltage: 2.5V to 5.5V

Wide Operating Temperature Range: -40°C to 125°C

• No Start-Up Initialization Required

Default Output High and Low Options

• High Electromagnetic Immunity

High CMTI: ±150kV/μs (Typical)

Low Power Consumption (Typical):

1.5mA per Channel at 1Mbps with 5.0V Supply

6.6mA per Channel at 100Mbps with 5.0V Supply

Precise Timing (Typical)

12ns Propagation Delay

1ns Pulse Width Distortion

2ns Propagation Delay Skew

5ns Minimum Pulse Width

Isolation Rating up to 5.7kVrms

ESD: ±8kV HBM

• Isolation Barrier Life: >40 Years

Schmitt Trigger Inputs

RoHS-Compliant Packages

SOIC16 Extra Wide Body

#### 2. Applications

• Industrial Automation Systems

Motor Control

Medical Electronics

Isolated Switch Mode Supplies

Solar Inverters

Isolated ADC, DAC

# 3. Description

The CA-IS3821 devices are high-performance dual - channel digital isolators with precise timing characteristics and low power consumption. The CA-IS3821 devices provide high electromagnetic immunity and low emissions, while

isolating CMOS digital I/Os. All device versions have Schmitt trigger input for high noise immunity. Each isolation channel consists of a transmitter and a receiver separated by silicon dioxide ( $SiO_2$ ) insulation barrier. The CA-IS3821 device has one forward and one reverse-direction channels. All devices have fail-safe mode option. If the input power or signal is lost, default output is low for devices with suffix L and high for devices with suffix H.

CA-IS3821 devices has high insulation capability to handle noise and surge on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. High CMTI ability promises the correct transmission of digital signal. The CA-IS382x devices are available in SOIC16 pin extra wide body. All products support insulation withstanding up to 5.7kVrms.

#### **Device Information**

| PART<br>NUMBER | PACKAGE            | BODY SIZE(NOM)      |

|----------------|--------------------|---------------------|

| CA-IS3821      | SOIC16-<br>WWB(WW) | 10.30 mm × 14.00 mm |

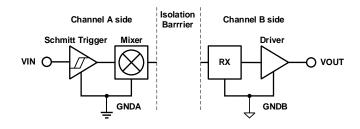

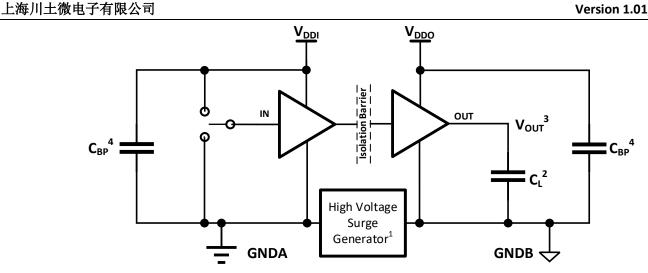

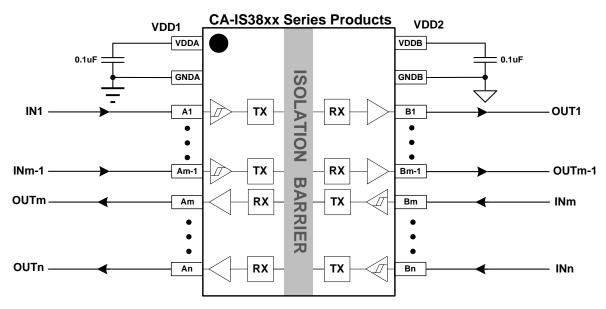

# **Simplified Channel Structure**

Channel A side and B side are separated by isolation capacitors. GNDA and GNDB are the isolated ground for signals and supplies of A side and B side respectively.

# 4. Ordering Guide

**Table 4-1 Ordering Guide for Valid Ordering Part Number**

| Ordering Part Number | Number of Inputs<br>A Side | Number of Inputs<br>B Side | Default Output | Isolation<br>Rating (kV) | Output<br>Enable | Package    |

|----------------------|----------------------------|----------------------------|----------------|--------------------------|------------------|------------|

| CA-IS3821LWW         | 2                          | 1                          | Low            | 5.7                      | No               | SOIC16-WWB |

| CA-IS3821HWW         | 2                          | 1                          | High           | 5.7                      | No               | SOIC16-WWB |

上海川土微电子有限公司

| L. | Key Feat  | tures                                 | 1 |

|----|-----------|---------------------------------------|---|

| 2. | Applicat  | ions                                  | 1 |

| 3. | Descript  | tion                                  | 1 |

| 1. | Orderin   | g Guide                               | 2 |

| 5. | Revision  | n History                             | 3 |

| 5. | PIN Des   | criptions and Functions               | 4 |

| 7. | Specifica | ations                                | 5 |

|    | 7.1.      | Absolute Maximum Ratings <sup>1</sup> | 5 |

|    | 7.2.      | ESD Ratings                           | 5 |

|    | 7.3.      | Recommended Operating Conditions      | 5 |

|    | 7.4.      | Thermal Information                   | 6 |

|    | 7.5.      | Power Rating                          | 6 |

|    | 7.6.      | Insulation Specifications             | 7 |

|    | 7.7.      | Safety-Related Certifications         | 8 |

|    | 7.8.      | Electrical Characteristics            | 9 |

$V_{DDA} = V_{DDB} = 5 \text{ V} \pm 10\%$ ,  $T_A = -40^{\circ}\text{C}$  to 125°C..9

$V_{DDA}$  =  $V_{DDB}$  = 3.3 V  $\pm$  10%,  $T_A$  = -40°C to 125°C

$V_{DDA}$  =  $V_{DDB}$  = 2.5 V ± 5%,  $T_A$  = -40°C to 125°C.9

|     | 7.9   | 9.2.      | $V_{DDA} = V_{DDB} = 3.3 \text{ V} \pm 10\%, T_A = -40^{\circ}\text{C to } 1$      | .25°C |

|-----|-------|-----------|------------------------------------------------------------------------------------|-------|

|     | 7.9   | 9.3.      | $V_{DDA} = V_{DDB} = 2.5 \text{ V} \pm 5\%$ , $T_A = -40^{\circ}\text{C}$ to 12 10 | .5°C  |

|     | 7.10. | Timi      | ng Characteristics                                                                 | 11    |

|     | 7.1   | LO.1.     | $V_{DDA} = V_{DDB} = 5 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 12!    | 5°C11 |

|     | 7.1   | 10.2.     | $V_{DDA} = V_{DDB} = 3.3 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 1 11 | .25°C |

|     | 7.1   | 10.3.     | $V_{DDA} = V_{DDB} = 2.5 \text{ V} \pm 5\%$ , $T_A = -40^{\circ}\text{C}$ to 12    | .5°C  |

| 8.  | Paran | neter M   | easurement Information                                                             | 12    |

| 9.  | Detai | led Des   | cription                                                                           | 14    |

|     | 9.1.  | Theo      | ory of Operation                                                                   | 14    |

|     | 9.2.  | Fund      | tional Block Diagram                                                               | 14    |

|     | 9.3.  | Devi      | ce Operation Modes                                                                 | 15    |

| 10. | Į.    | Applicati | ion and Implementation                                                             | 16    |

| 11. | F     | Package   | Information                                                                        | 17    |

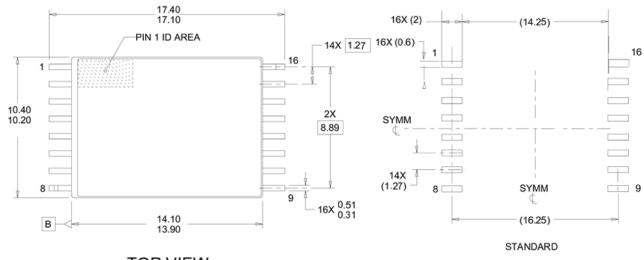

|     | 11.1. | 16-P      | in Extra Wide Body SOIC Package                                                    | 17    |

| 12. | 9     | Solderin  | g Information                                                                      | 18    |

| 13. | 1     | Tape And  | d Reel Information                                                                 | 19    |

| 14. |       |           | nt Notice                                                                          |       |

|     |       |           |                                                                                    |       |

# 5. Revision History

7.8.1. 7.8.2.

7.8.3.

7.9.1.

7.9.

| Version     | Revision history                                        | Page |

|-------------|---------------------------------------------------------|------|

| Version1.01 | Remove CA-IS382x parts except CA-IS3821HWW,CA-IS3821LWW | NA   |

# 6. PIN Descriptions and Functions

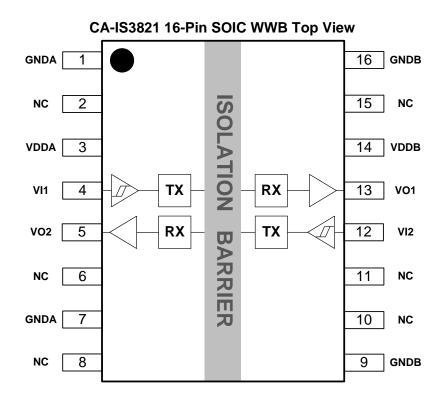

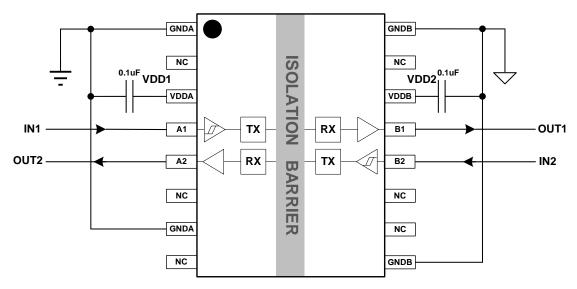

Figure 6-1 CA-IS3821 in 16-Pin SOIC Extra Wide Body Package Top View

Table 5-1 CA-IS3821 in 16-Pin SOIC Extra Wide Body Package Pin Description and Functions

| Name                        | SOIC-16 Pin#          | Type                 | Description                                                 |

|-----------------------------|-----------------------|----------------------|-------------------------------------------------------------|

| GNDA                        | 1                     | Ground               | Side A Ground                                               |

| NC                          | 2                     | No Connect           | No Connect                                                  |

| VDDA                        | 3                     | Supply               | Side A Power Supply                                         |

| VI1                         | 4                     | Digital I/O          | Side A Digital Input for CA-IS3821                          |

| VO2                         | 5                     | Digital I/O          | Side A Digital Output for CA-IS3821.                        |

| NC                          | 6                     | No Connect           | No Connect                                                  |

| GNDA                        | 7                     | Ground               | Side B Ground                                               |

| NC                          | 8                     | No Connect           | No Connect                                                  |

| GNDB                        | 9                     | Ground               | Side B Ground                                               |

| NC                          | 10                    | No Connect           | No Connect                                                  |

| NC                          | 11                    | No Connect           | No Connect                                                  |

| VI2                         | 12                    | Digital I/O          | Side B Digital Input for CA-IS3821                          |

| VO1                         | 13                    | Digital I/O          | Side B Digital Output for CA-IS3821                         |

| VDDB                        | 14                    | Supply               | Side B Power Supply                                         |

| NC                          | 15                    | No Connect           | No Connect                                                  |

| GNDB                        | 16                    | Ground               | Side B Ground                                               |

| <b>Note:</b><br>1. No Conne | ect. These pins are r | not internally conne | cted. They can be left floating, tied to VDD or tied to GND |

上海川土微电子有限公司

# **Specifications**

# 7.1. Absolute Maximum Ratings<sup>1</sup>

|                                     |                             | MIN  | MAX               | UNIT |

|-------------------------------------|-----------------------------|------|-------------------|------|

| V <sub>DDA</sub> , V <sub>DDB</sub> | Supply Voltage <sup>2</sup> | -0.5 | 6.0               | V    |

| V <sub>in</sub>                     | Voltage at Ax, Bx, ENx      | -0.5 | $V_{DDA} + 0.5^3$ | V    |

| l <sub>0</sub>                      | Output Current              | -20  | 20                | mA   |

| T <sub>J</sub>                      | Junction Temperature        |      | 150               | °C   |

| T <sub>STG</sub>                    | Storage Temperature         | -65  | 150               | °C   |

#### NOTE:

- 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GNDA or GNDB) and are peak voltage

- 3. Maximum voltage must not exceed 6 V.

# 7.2. ESD Ratings

|                                |                                                                                               | VALUE | UNIT |

|--------------------------------|-----------------------------------------------------------------------------------------------|-------|------|

| V <sub>ESD</sub> Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, to the Pins on the same side <sup>1</sup> | ±8000 | V    |

| discharge                      | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>2</sup>        | ±2000 | V    |

#### NOTE:

- JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Recommended Operating Conditions** 7.3.

|                                     |                                       |                         | MIN   | TYP  | MAX   | UNIT |

|-------------------------------------|---------------------------------------|-------------------------|-------|------|-------|------|

| V <sub>DDA</sub> , V <sub>DDB</sub> | Supply Voltage                        |                         | 2.375 | 3.3  | 5.5   | V    |

| V <sub>DD</sub> (UVLO+)             | VDD Undervoltage Threshold When Supp  | ly Voltage is Rising    | 1.95  | 2.24 | 2.375 | V    |

| V <sub>DD</sub> (UVLO-)             | VDD Undervoltage Threshold When Supp  | ly Voltage is Falling   | 1.88  | 2.10 | 2.325 | V    |

| V <sub>HYS</sub> (UVLO)             | VDD Undervoltage Threshold Hysteresis |                         | 70    | 140  | 250   | mV   |

|                                     |                                       | $V_{DDO}^1 = 5V$        | -4    |      |       |      |

| I <sub>OH</sub>                     | High-level Output Current             | V <sub>DDO</sub> = 3.3V | -2    |      |       | mA   |

|                                     |                                       | V <sub>DDO</sub> = 2.5V | -1    |      |       | 1    |

|                                     | Low-level Output Current              | V <sub>DDO</sub> = 5V   |       |      | 4     |      |

| I <sub>OL</sub>                     |                                       | V <sub>DDO</sub> = 3.3V |       |      | 2     | mA   |

|                                     |                                       | V <sub>DDO</sub> = 2.5V |       |      | 1     |      |

| V <sub>IH</sub>                     | High-level Input Voltage              |                         | 2.0   |      |       | V    |

| V <sub>IL</sub>                     | Low-level Input Voltage               |                         |       |      | 0.8   | V    |

| DR                                  | Data Rate                             |                         | 0     |      | 150   | Mbps |

| T <sub>A</sub>                      | Ambient Temperature                   |                         | -40   | 27   | 125   | °C   |

| NOTE:                               |                                       |                         | •     |      |       | •    |

$V_{DDO}$  = Output-side  $V_{DD}$

# 7.4. Thermal Information

|                  | THERMAL METRIC                         | CA-IS3821 | UNIT |

|------------------|----------------------------------------|-----------|------|

|                  | THERIVIAL WILLTRIC                     | ww        | ONIT |

| R <sub>θJA</sub> | Junction-to-ambient thermal resistance | 83.4      | °C/W |

# 7.5. Power Rating

|                 | PARAMETER                           | TEST CONDITIONS                                            | MIN | TYP | MAX | UNIT |

|-----------------|-------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| CA-IS38         | 221                                 |                                                            |     |     |     |      |

| P <sub>D</sub>  | Maximum Power Dissipation           | $V_{DDA} = V_{DDB} = 5.5 \text{ V, } C_L = 15 \text{ pF,}$ |     |     | 120 | mW   |

| P <sub>DA</sub> | Maximum Power Dissipation on Side-A | T <sub>J</sub> = 150°C, Input a 75-MHz 50% duty            |     |     | 60  | mW   |

| P <sub>DB</sub> | Maximum Power Dissipation on Side-B | cycle square wave                                          |     |     | 60  | mW   |

# 7.6. Insulation Specifications

上海川土微电子有限公司

|                   | PARAMETR                                          | TEST CONDITIONS                                                                                                                                                                                                                         | VALUE<br>WW | UNIT             |

|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------|

| CLR               | External clearance <sup>1</sup>                   | Shortest terminal-to-terminal distance through air                                                                                                                                                                                      | >15         | mm               |

| CPG               | External creepage <sup>1</sup>                    | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                                       | >15         | mm               |

| DTI               | Distance through the insulation                   | Minimum internal gap (internal clearance)                                                                                                                                                                                               | >27         | μm               |

| CTI               | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                                                                   | >600        | V                |

|                   | Material group                                    | According to IEC 60664-1                                                                                                                                                                                                                | I           |                  |

|                   |                                                   | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                                                                              | I-IV        |                  |

|                   | Overvoltage category per IEC 60664-1              | Rated mains voltage ≤ 400 V <sub>RMS</sub>                                                                                                                                                                                              | I-IV        | 1                |

|                   |                                                   | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                              | I-III       | 1                |

| DIN V VD          | DE V 0884-11:2017-01 <sup>2</sup>                 |                                                                                                                                                                                                                                         |             |                  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                                                                                                                                                                                    | 2828        | V <sub>PK</sub>  |

| V <sub>IOWM</sub> | Maximum working isolation voltage                 | AC voltage; Time dependent dielectric breakdown (TDDB) Test                                                                                                                                                                             | 2000        | V <sub>RMS</sub> |

|                   | , , , , , , , , , , , , , , , , , , ,             | DC voltage                                                                                                                                                                                                                              | 2828        | $V_{DC}$         |

| V <sub>IOTM</sub> | Maximum transient isolation voltage               | V <sub>TEST</sub> = V <sub>IOTM</sub> ,<br>t = 60 s (qualification);<br>V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> ,<br>t= 1 s (100% production)                                                                                       | 8000        | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>3</sup>      | Test method per IEC 60065, 1.2/50 $\mu$ s waveform,<br>$V_{\text{TEST}} = 1.6 \times V_{\text{IOSM}}$ (qualification)                                                                                                                   | 8000        | V <sub>PK</sub>  |

|                   |                                                   | Method a, After Input/Output safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10$ s                                                                                        | ≤5          |                  |

| q <sub>pd</sub>   | Apparent charge <sup>4</sup>                      | Method a, After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10$ s                                                                                               | ≤5          | pC               |

|                   |                                                   | Method b1, At routine test (100% production) and preconditioning (type test) $V_{\text{ini}} = 1.2 \times V_{\text{IOTM}}, t_{\text{ini}} = 1 \text{ s};$ $V_{\text{pd(m)}} = 1.875 \times V_{\text{IORM}}, t_{\text{m}} = 1 \text{ s}$ | ≤5          | -                |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>5</sup> | $V_{10} = 0.4 \times \sin(2\pi ft), f = 1 \text{ MHz}$                                                                                                                                                                                  | ~0.5        | pF               |

|                   | , h                                               | V <sub>10</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                                          | >1012       |                  |

| R <sub>IO</sub>   | Isolation resistance <sup>5</sup>                 | $V_{10} = 500 \text{ V}, 100^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$                                                                                                                                                         | >1011       | Ω                |

|                   |                                                   | V <sub>10</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                                                       | >109        | 1                |

|                   | Pollution degree                                  |                                                                                                                                                                                                                                         | 2           | †                |

| UL 1577           | 0                                                 |                                                                                                                                                                                                                                         | 1           |                  |

| V <sub>ISO</sub>  | Maximum withstanding isolation voltage            | $V_{TEST} = V_{ISO}$ , $t = 60$ s (qualification),<br>$V_{TEST} = 1.2 \times V_{ISO}$ , $t = 1$ s (100% production)                                                                                                                     | 5700        | V <sub>RMS</sub> |

- Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed circuit board are used to help increase these specifications.

- 2. This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- 3. Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- 4. Apparent charge is electrical discharge caused by a partial discharge (pd).

- All pins on each side of the barrier tied together creating a two-terminal device.

# 7.7. Safety-Related Certifications

| VDE(Pending)                      | CSA(Pending)               | UL(Pending)           | CQC(Pending)           | TUV(Pending)              |

|-----------------------------------|----------------------------|-----------------------|------------------------|---------------------------|

| Certified according to DIN        | Certified according to IEC | Recognized under UL   | Certified according to | Certified according to EN |

| V VDE V 0884-11:2017-01           | 60950-1, IEC 62368-1 and   | 1577 Component        | GB4943.1-2011          | 61010-1:2010 (3rd Ed)     |

|                                   | IEC 60601-1                | Recognition Program   |                        | and EN 60950-             |

|                                   |                            |                       |                        | 1:2006/A2:2013            |

| Maximum transient                 |                            | SOIC16-WWB: 5700 VRMS |                        |                           |

| isolation voltage,                |                            |                       |                        |                           |

| 8000V <sub>pk</sub> (SOIC16-WWB), |                            |                       |                        |                           |

| Certification number:             | Certification number:      | Certification number: | Certification number:  | Certification number:     |

#### **Electrical Characteristics**

上海川土微电子有限公司

# 7.8.1. $V_{DDA} = V_{DDB} = 5 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

|                      | PARAMETER                        | TEST CONDITIONS                                                              | MIN                                | TYP | MAX | UNIT  |

|----------------------|----------------------------------|------------------------------------------------------------------------------|------------------------------------|-----|-----|-------|

| V <sub>OH</sub>      | High-level Output Voltage        | I <sub>OH</sub> = -4mA; See Figure 7-1                                       | V <sub>DDO</sub> <sup>1</sup> -0.4 | 4.8 |     | V     |

| V <sub>OL</sub>      | Low-level Output Voltage         | I <sub>OL</sub> = 4mA; <i>See Figure 7-1</i>                                 |                                    | 0.2 | 0.4 | V     |

| V <sub>IT+(IN)</sub> | Positive-going Input Threshold   |                                                                              | 2                                  |     |     | V     |

| V <sub>IT-(IN)</sub> | Negative-going Input Threshold   |                                                                              |                                    |     | 0.8 | V     |

| I <sub>IH</sub>      | High-Level Input Leakage Current | V <sub>IH</sub> = V <sub>DDA</sub> at Ax or Bx or ENx                        |                                    |     | 20  | μΑ    |

| I <sub>IL</sub>      | Low-Level Input Leakage Current  | V <sub>IL</sub> = 0 V at Ax or Bx                                            | -20                                |     |     | μΑ    |

| Zo                   | Output Impedance <sup>2</sup>    |                                                                              |                                    | 50  |     | Ω     |

| CMTI                 | Common-mode Transient Immunity   | $V_{I} = V_{DDI}^{1}$ or 0 V, $V_{CM} = 1200$ V; See Figure 7-3              | 100                                | 150 |     | kV/μS |

| Cı                   | Input Capacitance <sup>3</sup>   | $V_I = V_{DD}/2 + 0.4 \times \sin(2\pi ft)$ , $f = 1$ MHz,<br>$V_{DD} = 5$ V |                                    | 2   |     | pF    |

# NOTE:

- $V_{DDI}$  = Input-side  $V_{DD}$ ,  $V_{DDO}$  = Output-side  $V_{DD}$

- The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$  ± 40%.

- Measured from pin to Ground.

# 7.8.2. $V_{DDA} = V_{DDB} = 3.3 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

|                      | PARAMETER                        | TEST CONDITIONS                                                                             | MIN                                | TYP | MAX | UNIT  |

|----------------------|----------------------------------|---------------------------------------------------------------------------------------------|------------------------------------|-----|-----|-------|

| V <sub>OH</sub>      | High-level Output Voltage        | I <sub>OH</sub> = -4mA; See Figure 7-1                                                      | V <sub>DDO</sub> <sup>1</sup> -0.2 | 3.1 |     | V     |

| V <sub>OL</sub>      | Low-level Output Voltage         | I <sub>OL</sub> = 4mA; See Figure 7-1                                                       |                                    | 0.2 | 0.4 | V     |

| V <sub>IT+(IN)</sub> | Positive-going Input Threshold   |                                                                                             | 2                                  |     |     | V     |

| V <sub>IT-(IN)</sub> | Negative-going Input Threshold   |                                                                                             |                                    |     | 0.8 | V     |

| I <sub>IH</sub>      | High-Level Input Leakage Current | V <sub>IH</sub> = V <sub>DDA</sub> at Ax or Bx or ENx                                       |                                    |     | 20  | μΑ    |

| I <sub>IL</sub>      | Low-Level Input Leakage Current  | V <sub>IL</sub> = 0 V at Ax or Bx                                                           | -20                                |     |     | μΑ    |

| Zo                   | Output Impedance <sup>2</sup>    |                                                                                             |                                    | 50  |     | Ω     |

| CMTI                 | Common-mode Transient Immunity   | $V_1 = V_{DD1}^1$ or 0 V, $V_{CM} = 1200$ V; See Figure 7-3                                 |                                    | 100 | 150 | kV/μs |

| Cı                   | Input Capacitance <sup>3</sup>   | $V_I = V_{DD}/2 + 0.4 \times \sin(2\pi ft), f = 1 \text{ MHz},$<br>$V_{DD} = 3.3 \text{ V}$ |                                    | 2   |     | pF    |

# NOTE:

- $V_{DDI}$  = Input-side  $V_{DD,}$   $V_{DDO}$  = Output-side  $V_{DD}$ 1.

- The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$  ± 40%.

- Measured from pin to Ground.

# 7.8.3. $V_{DDA} = V_{DDB} = 2.5 \text{ V} \pm 5\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

|                      | PARAMETER                        | TEST CONDITIONS                                                     | MIN                                | TYP | MAX | UNIT  |

|----------------------|----------------------------------|---------------------------------------------------------------------|------------------------------------|-----|-----|-------|

| V <sub>OH</sub>      | High-level Output Voltage        | I <sub>OH</sub> = -4mA; See Figure 7-1                              | V <sub>DDO</sub> <sup>1</sup> -0.4 | 2.3 |     | V     |

| V <sub>OL</sub>      | Low-level Output Voltage         | I <sub>OL</sub> = 4mA; See Figure 7-1                               |                                    | 0.2 | 0.4 | V     |

| V <sub>IT+(IN)</sub> | Positive-going Input Threshold   |                                                                     | 2                                  |     |     | V     |

| V <sub>IT-(IN)</sub> | Negative-going Input Threshold   |                                                                     |                                    |     | 0.8 | V     |

| I <sub>IH</sub>      | High-Level Input Leakage Current | $V_{IH} = V_{DDA}$ at Ax or Bx or ENx                               |                                    |     | 20  | μΑ    |

| I <sub>IL</sub>      | Low-Level Input Leakage Current  | V <sub>IL</sub> = 0 V at Ax or Bx                                   | -20                                |     |     | μΑ    |

| Zo                   | Output Impedance <sup>2</sup>    |                                                                     |                                    | 50  |     | Ω     |

| CMTI                 | Common-mode Transient Immunity   | $V_1 = V_{DD1}^1$ or 0 V, $V_{CM} = 1200$ V; See Figure 7-3         | 100                                | 150 |     | kV/μS |

| Cı                   | Input Capacitance <sup>3</sup>   | $V_1 = V_{DD}/2 + 0.4 \times \sin(2\pi ft)$ , $f = 1 \text{ MHz}$ , |                                    | 2   |     | nΕ    |

|                      |                                  | V <sub>DD</sub> = 2.5 V                                             |                                    |     |     | pF    |

- $V_{DDI}$  = Input-side  $V_{DD,}V_{DDO}$  = Output-side  $V_{DD}$

- The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$  ± 40%. 2.

- Measured from pin to Ground.

# 7.9. Supply Current Characteristics

# 7.9.1. $V_{DDA} = V_{DDB} = 5 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

| PARAMETER              | TEST CONDITION                       | SUPPLY<br>CURRENT | MIN              | ТҮР | MAX  | UNIT |    |

|------------------------|--------------------------------------|-------------------|------------------|-----|------|------|----|

| -IS3821                |                                      |                   |                  |     |      |      |    |

|                        | V <sub>IN</sub> = 0V (CA-IS3821L);   |                   | I <sub>DDA</sub> |     | 1.6  | 3.2  |    |

| Supply Curr2.0ent – DC | $V_{IN} = V_{DDI}$ (CA-IS3821H)      |                   | I <sub>DDB</sub> |     | 1.6  | 3.2  |    |

| Signal                 | $V_{IN} = V_{DDI}$ (CA-IS3821L);     |                   | I <sub>DDA</sub> |     | 2.9  | 5.8  |    |

|                        | $V_{IN} = OV(CA-IS3821H)$            |                   | I <sub>DDB</sub> |     | 2.9  | 5.8  |    |

|                        |                                      | 1Mbps             | I <sub>DDA</sub> |     | 2.1  | 3.2  | Ī  |

|                        | All Channels Switching with 50%      | (500kHz)          | I <sub>DDB</sub> |     | 2.1  | 3.2  | mA |

| Supply Curre3.1nt – AC | Duty Cycle Square Wave Clock Input   | 10Mbps            | I <sub>DDA</sub> |     | 5.6  | 7.8  |    |

| Signal                 | with 5V Amplitude; $C_L = 15$ pF for | (5MHz)            | I <sub>DDB</sub> |     | 5.6  | 7.8  |    |

|                        | Each Channel                         | 100Mbps           | I <sub>DDA</sub> |     | 12.9 | 22   |    |

|                        |                                      | (50MHz)           | I <sub>DDB</sub> |     | 12.9 | 22   |    |

# 7.9.2. $V_{DDA} = V_{DDB} = 3.3 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

| PARAMETER                                        | TEST CONDITION                                   | SUPPLY<br>CURRENT | MIN              | ТҮР | MAX | UNIT |    |

|--------------------------------------------------|--------------------------------------------------|-------------------|------------------|-----|-----|------|----|

| CA-IS3821                                        |                                                  |                   |                  |     |     |      |    |

|                                                  | V <sub>IN</sub> = 0V (CA-IS3821L);               |                   | I <sub>DDA</sub> |     | 1.2 | 1.9  |    |

| Supply Current – DC Signal                       | $V_{IN} = V_{DDI}$ (CA-IS3821H)                  |                   | I <sub>DDB</sub> |     | 1.2 | 1.9  |    |

| Supply Current – DC Signal                       | V <sub>IN</sub> = V <sub>DDI</sub> (CA-IS3821L); |                   | I <sub>DDA</sub> |     | 2.3 | 3.3  |    |

|                                                  | $V_{IN} = OV(CA-IS3821H)$                        |                   | I <sub>DDB</sub> |     | 2.3 | 3.3  |    |

|                                                  |                                                  | 1Mbps             | I <sub>DDA</sub> |     | 1.9 | 2.9  | mA |

|                                                  | All Channels Switching with 50%                  | (500kHz)          | I <sub>DDB</sub> |     | 1.9 | 2.9  | ma |

| Supply Current AC Signal                         | Duty Cycle Square Wave Clock Input               | 10Mbps            | I <sub>DDA</sub> |     | 4.2 | 5.9  |    |

| Supply Current – AC Signal                       | with 5V Amplitude; $C_L = 15$ pF for             | (5MHz)            | I <sub>DDB</sub> |     | 4.2 | 5.9  |    |

|                                                  | Each Channel                                     | 100Mbps           | I <sub>DDA</sub> |     | 8.8 | 12.1 |    |

|                                                  |                                                  | (50MHz)           | I <sub>DDB</sub> |     | 8.8 | 12.1 |    |

| Note:                                            |                                                  |                   |                  |     |     |      |    |

| 1. V <sub>DDI</sub> = Input-side V <sub>DD</sub> |                                                  |                   |                  |     |     |      |    |

# 7.9.3. $V_{DDA} = V_{DDB} = 2.5 \text{ V} \pm 5\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

| PARAMETER                  | TEST CONDITION                                   | SUPPLY<br>CURRENT | MIN              | ТҮР | MAX | UNIT |      |

|----------------------------|--------------------------------------------------|-------------------|------------------|-----|-----|------|------|

| A-IS3821                   |                                                  |                   |                  |     |     |      |      |

|                            | V <sub>IN</sub> = 0V (CA-IS3821L);               |                   | I <sub>DDA</sub> |     | 1.5 | 1.9  |      |

| Cumply Current DC Cianal   | $V_{IN} = V_{DDI}$ (CA-IS3821H)                  |                   | I <sub>DDB</sub> |     | 1.5 | 1.9  |      |

| Supply Current – DC Signal | V <sub>IN</sub> = V <sub>DDI</sub> (CA-IS3821L); |                   | I <sub>DDA</sub> |     | 2.1 | 3.1  |      |

|                            | $V_{IN} = 0V(CA-IS3821H)$                        |                   | I <sub>DDB</sub> |     | 2.1 | 3.1  |      |

|                            |                                                  | 1Mbps             | I <sub>DDA</sub> |     | 1.9 | 2.8  | mA   |

|                            | All Channels Switching with 50%                  | (500kHz)          | I <sub>DDB</sub> |     | 1.9 | 2.8  | IIIA |

| Supply Current – AC Signal | Duty Cycle Square Wave Clock Input               | 10Mbps            | I <sub>DDA</sub> |     | 3.6 | 5.2  |      |

| Supply Current – AC Signal | with 5V Amplitude; $C_L = 15$ pF for             | (5MHz)            | I <sub>DDB</sub> |     | 3.6 | 5.2  |      |

|                            | Each Channel                                     | 100Mbps           | I <sub>DDA</sub> |     | 6.9 | 9.5  |      |

|                            |                                                  | (50MHz)           | I <sub>DDB</sub> |     | 6.9 | 9.5  |      |

# 上海川土微电子有限公司 7.10. Timing Characteristics

# 7.10.1. $V_{DDA} = V_{DDB} = 5 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

|                                     | PARAMETER                                                    | TEST CONDITIONS | MIN | TYP  | MAX  | UNIT |

|-------------------------------------|--------------------------------------------------------------|-----------------|-----|------|------|------|

| DR                                  | Data Rate                                                    |                 | 0   |      | 150  | Mbps |

| PW <sub>min</sub>                   | Minimum Pulse Width                                          |                 |     |      | 5.0  | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay Time                                       | Con Figure 9.1  | 5.0 | 12.0 | 15.0 | ns   |

| PWD                                 | Pulse Width Distortion   t <sub>PLH</sub> - t <sub>PHL</sub> | See Figure 8-1  |     | 0.2  | 4.5  | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel Output Skew Time <sup>1</sup>             | Same-direction  |     | 0.4  | 2.5  | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part Skew Time <sup>2</sup>                          |                 |     | 2.0  | 4.5  | ns   |

| t <sub>r</sub>                      | Output Signal Rise Time                                      | See Figure 8-1  |     | 2.5  | 4.0  | ns   |

| t <sub>f</sub>                      | Output Signal Fall Time                                      | See Figure 8-1  |     | 2.5  | 4.0  | ns   |

| t <sub>DO</sub>                     | Default Output Delay Time from Input Power Loss              | See Figure 8-2  |     | 8    | 12   | ns   |

| t <sub>SU</sub>                     | Start-up Time                                                |                 |     | 15   | 40   | μs   |

|                                     |                                                              | See rigule 6-2  |     |      |      |      |

#### NOTE:

- $t_{sk(0)}$  is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

- tsk(pp) is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

# 7.10.2. $V_{DDA} = V_{DDB} = 3.3 \text{ V} \pm 10\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

|                                     | PARAMETER                                                    | TEST CONDITIONS | MIN | TYP  | MAX  | UNIT |

|-------------------------------------|--------------------------------------------------------------|-----------------|-----|------|------|------|

| DR                                  | Data Rate                                                    |                 | 0   |      | 150  | Mbps |

| $PW_{min}$                          | Minimum Pulse Width                                          |                 |     |      | 5.0  | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay Time                                       | Can Figure 9 1  | 5.0 | 12.0 | 15.0 | ns   |

| PWD                                 | Pulse Width Distortion   t <sub>PLH</sub> - t <sub>PHL</sub> | See Figure 8-1  |     | 0.2  | 4.5  | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel Output Skew Time <sup>1</sup>             | Same-direction  |     | 0.4  | 2.5  | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part Skew Time <sup>2</sup>                          |                 |     | 2.0  | 4.5  | ns   |

| t <sub>r</sub>                      | Output Signal Rise Time                                      | See Figure 8-1  |     | 2.5  | 4.0  | ns   |

| t <sub>f</sub>                      | Output Signal Fall Time                                      | See Figure 8-1  |     | 2.5  | 4.0  | ns   |

| t <sub>DO</sub>                     | Default Output Delay Time from Input Power Loss              | See Figure 8-2  |     | 8    | 12   | ns   |

| t <sub>SU</sub>                     | Start-up Time                                                |                 |     | 15   | 40   | μs   |

#### NOTE:

- t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

- t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

#### 7.10.3. $V_{DDA} = V_{DDB} = 2.5 \text{ V} \pm 5\%$ , $T_A = -40^{\circ}\text{C}$ to 125°C

|                                     | PARAMETER                                                    | TEST CONDITIONS | MIN | TYP  | MAX  | UNIT |

|-------------------------------------|--------------------------------------------------------------|-----------------|-----|------|------|------|

| DR                                  | Data Rate                                                    |                 | 0   |      | 150  | Mbps |

| $PW_{min}$                          | Minimum Pulse Width                                          |                 |     |      | 5.0  | ns   |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay Time                                       | Can Figure 9 1  | 5.0 | 12.0 | 15.0 | ns   |

| PWD                                 | Pulse Width Distortion   t <sub>PLH</sub> - t <sub>PHL</sub> | See Figure 8-1  |     | 0.2  | 5.0  | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel Output Skew Time <sup>1</sup>             | Same-direction  |     | 0.4  | 2.5  | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part Skew Time <sup>2</sup>                          |                 |     | 2.0  | 5.0  | ns   |

| t <sub>r</sub>                      | Output Signal Rise Time                                      | See Figure 8-1  |     | 2.5  | 4.0  | ns   |

| t <sub>f</sub>                      | Output Signal Fall Time                                      | See Figure 8-1  |     | 2.5  | 4.0  | ns   |

| t <sub>DO</sub>                     | Default Output Delay Time from Input Power Loss              | See Figure 8-2  |     | 8    | 12   | ns   |

| t <sub>SU</sub>                     | Start-up Time                                                |                 |     | 15   | 40   | μs   |

|                                     |                                                              |                 |     |      |      |      |

- t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

- t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

# CHIPANALOG

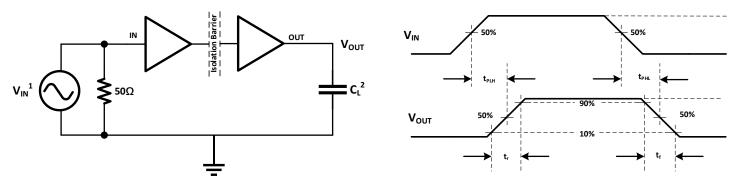

#### 8. Parameter Measurement Information

#### NOTE:

- 1. A square wave generator generate the  $V_{IN}$  input signal with the following constraints: waveform frequency  $\leq$  100kHz, 50% duty cycle,  $t_r \leq 3$ ns,  $t_f \leq 3$ ns. Since the waveform generator has an output impedance of  $Z_{out} = 50\Omega$ , the  $50\Omega$  resistor in the figure is used for matching. There is no need in the actual application.

- 2. C<sub>L</sub> is the load capacitance about 15pF together with the instrumentation capacitance. Since the load capacitance influence the output rising time, it's a key factor in the timing characteristic measurement.

Figure 8-1 Timing Characteristics Test Circuit and Voltage Waveforms

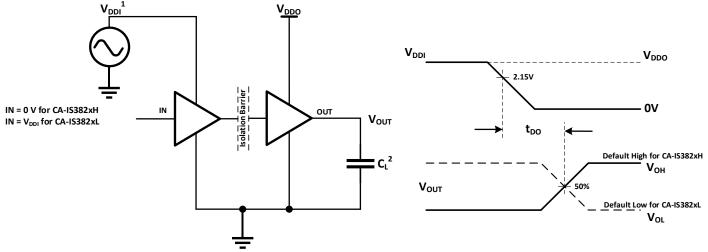

- 1. Power Supply Ramp Rate = 10 mV/ns.  $V_{DDI}$  should ramp over 2.375V but no higher than 5.5V.

- 2. C<sub>L</sub> is the load capacitance about 15pF together with the instrumentation capacitance. Since the load capacitance influence the output rising time, it's a key factor in the timing characteristic measurement.

Figure 8-2 Default Output Delay Time Test Circuit and Voltage Waveforms

- The High Voltage Surge Generator generates repetitive high voltage surges with > 1kV amplitude and <10ns rise time and 1. fall time to reach common-mode transient noise with > 150kV/ $\mu$ s slew rate.

- C<sub>L</sub> is the load capacitance about 15pF together with the instrumentation capacitance. 2.

- Pass-fail criteria: The output must remain stable whenever the high voltage surges come. 3.

- $C_{BP}$  is the 0.1 ~ 1uF bypass capacitance. 4.

Figure 8-3 Common-Mode Transient Immunity Test Circuit

## 9. Detailed Description

# 9.1. Theory of Operation

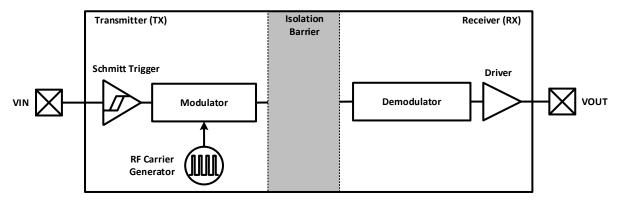

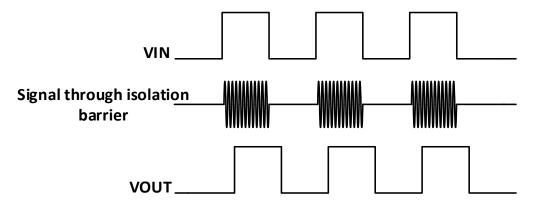

The CA-IS38xx family of devices use a simple ON-OFF keying (OOK) modulation scheme to transmit signal across the SiO<sub>2</sub> isolation capacitors that provide a robust insulation between two different voltage domain and act as a high frequency signal path between the input and the output. The transmitter (TX) modulates the input signal onto the carrier frequency, that is, TX delivers high frequency signal across the isolation barrier in one input state and delivers no signal across the barrier in the other input state. Then the receiver rebuilds the input signal according to the detected in-band energy. This simple architecture offers a robust isolated data path and requires no special considerations or initialization at start-up. The capacitor-based signal path is fully differential to maximize noise immunity, which is also known as common-mode transient immunity. Advanced circuitry techniques are applied for better EMI introduced by the carrier signal and IO switching. The capacitively-coupled architecture provides much higher electromagnetic immunity compared to the inductively-coupled one. And OOK modulation scheme eliminates the missing-pulse error that occurs in the pulse modulation method. A simplified functional block diagram and conceptual operation waveforms of a single channel is shown in Figure 9-1 and Figure 9-2.

#### 9.2. Functional Block Diagram

Figure 9-1 Functional Block Diagram of a Single Channel

Figure 9-2 Conceptual Operation Waveforms of a Single Channel

# 9.3. Device Operation Modes

上海川土微电子有限公司

Table 9-1 provides the operation modes for the CA-IS3821 devices.

# Table 9- 1 Operation Mode Table<sup>1</sup>

| $V_{DDI}$ | $V_{DDO}$ | INPUT(Ax/Bx) <sup>2</sup> | OUTPUT (Ax/Bx) | OPERATION                                                                                   |

|-----------|-----------|---------------------------|----------------|---------------------------------------------------------------------------------------------|

|           |           | Н                         | Н              | Normal operation mode:                                                                      |

|           |           | L                         | L              | A channel's output follows the input state                                                  |

| PU        | PU        |                           |                | Default output fail-safe mode:                                                              |

|           |           | Open                      | Default        | If a channel's input is left open, its output goes to the default value (Low for CA-IS382xL |

|           |           |                           |                | and High for CA-IS382xH).                                                                   |

|           |           |                           |                | Default output fail-safe mode:                                                              |

| PD        | PU        | Χ                         | Default        | If the input side VDD is unpowered, the outputs go in to the default output fail-safe mode  |

|           |           |                           |                | (Low for CA-IS382xL and High for CA-IS382xH)                                                |

| Х         | PD        | Х                         | Undetermined   | If the output side VDD is unpowered, the outputs' states are undetermined. <sup>3</sup>     |

- 1.  $V_{DDI}$  = Input-side  $V_{DD}$ ;  $V_{DDO}$  = Output-side  $V_{DD}$ ; PU = Powered up (VCC  $\geq$  2.375 V); PD = Powered down (VCC  $\leq$  2.25 V); X = Irrelevant; H = High level; L = Low level.

- 2. A strongly driven input signal can weakly power the floating V<sub>DD</sub> through an internal protection diode and cause undetermined output.

- The outputs are in undetermined state when 2.25V <  $V_{DDI}$ ,  $V_{DDO}$  < 2.375 V.

## 10. Application and Implementation

Unlike optocouplers, which need external components to improve performance, provide bias, or limit current, the CA-IS382x family device CMOS digital isolator needs only two external VDD bypass capacitors ( $0.1\mu\text{F}$  to  $1~\mu\text{F}$ ) to operate. Its TTL level compatible input terminals draw only micro amps of leakage current, allowing them to be driven without external buffering circuits. The output terminals have a characteristic impedance of 50  $\Omega$  (rail-to-rail swing) and are available in both forward and reverse channel configurations. Figure 10-1 shows the typical application schematic of CA-IS3821. And the circuit of Figure 10-2 is typical for most applications of CA-IS38xx series products and is as easy to use as a standard logic gate.

Figure 10-1 CA-IS3821 Digital Isolator Application Schematic

Figure 10-2 CA-IS38xx Series Digital Isolator Application Schematic

# 上海川土微电子有限公司 11. Package Information

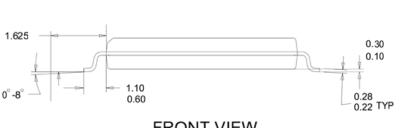

# 11.1. 16-Pin Extra Wide Body SOIC Package

The figure below illustrates the package details and the recommended land pattern details for the CA-IS382x digital isolator in a 16-pin extra wide body SOIC package. The values for the dimensions are shown in millimeters.

**TOP VIEW**

RECOMMENDED LAND PATTERN

**FRONT VIEW**

SIDE VIEW

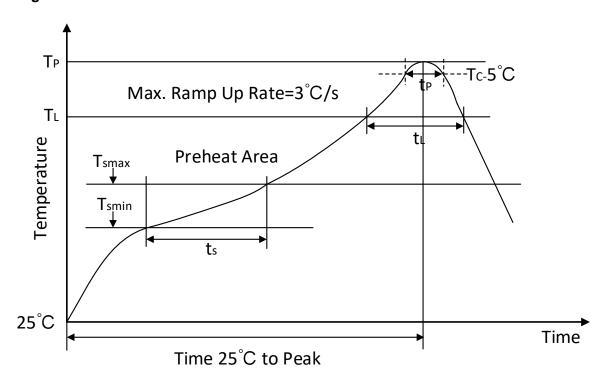

# 12. Soldering Information

Figure 12-1 Soldering Temperature (reflow) Profile

**Table12-1 Soldering Temperature Parameter**

| Profile Feature                             | Pb-Free Assembly  |

|---------------------------------------------|-------------------|

| Average ramp-up rate(217 °C to Peak)        | 3°C /second max   |

| Time of Preheat temp(from 150 °C to 200 °C) | 60-120 second     |

| Time to be maintained above 217 °C          | 60-150 second     |

| Peak temperature                            | 260 +5/-0 °C      |

| Time within 5°C of actual peak temp         | 30 second         |

| Ramp-down rate                              | 6 °C /second max. |

| Time from 25°C to peak temp                 | 8 minutes max     |

# 13. Tape And Reel Information

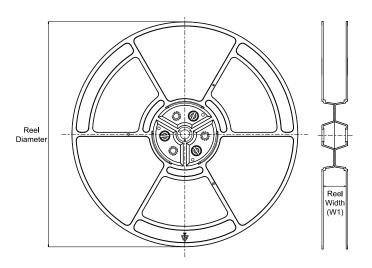

# **REEL DIMENSIONS**

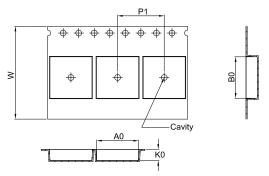

# **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

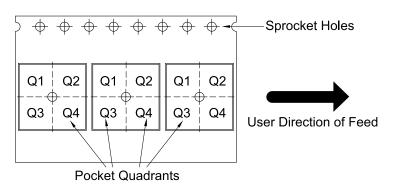

#### **QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Packa<br>ge<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|---------------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IS3821LWW | SOIC                | WW                 | 16   | 1000 | 330                      | 24.4                     | 10.7       | 17.7       | 3.1        | 16.0       | 24.0      | Q1               |

| CA-IS3821HWW | SOIC                | WW                 | 16   | 1000 | 330                      | 24.4                     | 10.7       | 17.7       | 3.1        | 16.0       | 24.0      | Q1               |

#### 14. Important Notice

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

#### **Trademark Information**

Chipanalog Inc. ®, Chipanalog® are trademarks or registered trademarks of Chipanalog.

http://www.chipanalog.com